芯实践第12期-数字芯片后端设计项目实践

Hide

Event DetailsHide...

芯动力人才计划® 芯实践第12期 数字芯片后端设计项目实践

01 组织单位 主办单位 上海芯聚辉、芯动力人才计划®项目办公室、新微创源孵化器 支持单位 SEMI China、上海ICC(上海集成电路技术与产业促进中心)、上海清华国际创新中心、南京集成电路产业服务中心(ICisC)、清华大学上海校友会半导体专委会、浦东工业技术研究院、广东省集成电路行业协会、南京集成电路行业协会、浙江省半导体行业协会、安徽省半导体行业协会、无锡集成电路学会、成都集成电路行业协会、杭州国家芯火平台、合肥国际芯火双创平台、成都国家芯火双创基地、第三代半导体产业技术战略联盟、求是缘半导体联盟 支持媒体 芯榜、是说芯语、半导体行业联盟、半导体行业观察、半导体圈、是说芯语、全球电子市场、半导体产业联盟、中国半导体论坛、半导体行业圈、半导体技术天地、芯思想、芯师爷、科钛网、芯科技等、电子创新网、大半导体产业网

02 课程亮点 ►真实企业项目及工程环境,亲身体验数字芯片后端设计工程实践。 ►8年+资深企业工程师指导及后续交流。 ►掌握数字芯片后端设计流程及对应的EDA工具。

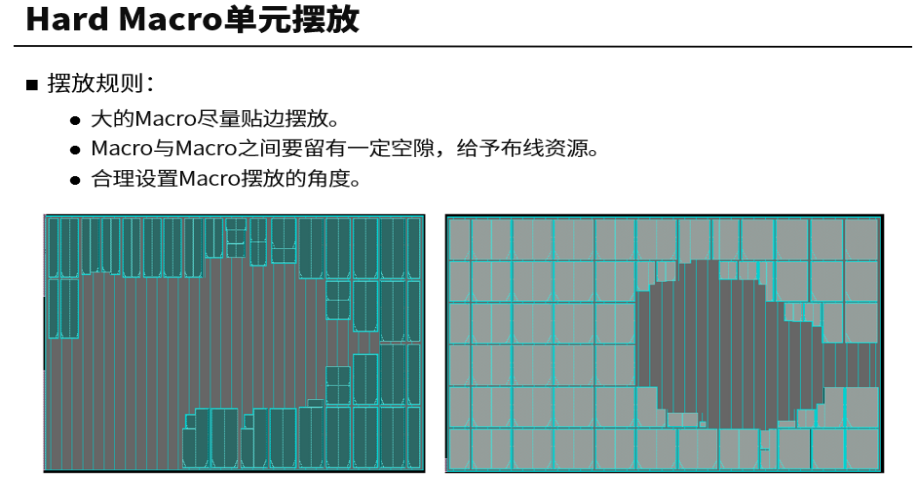

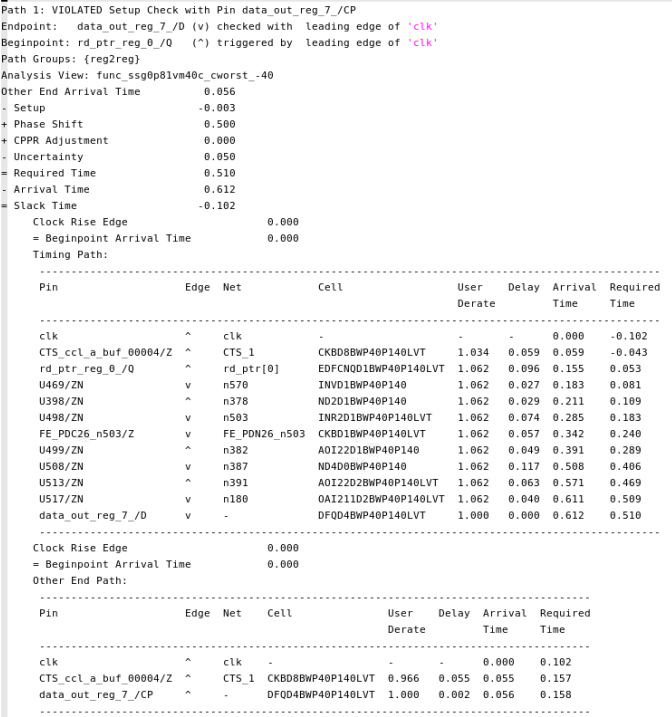

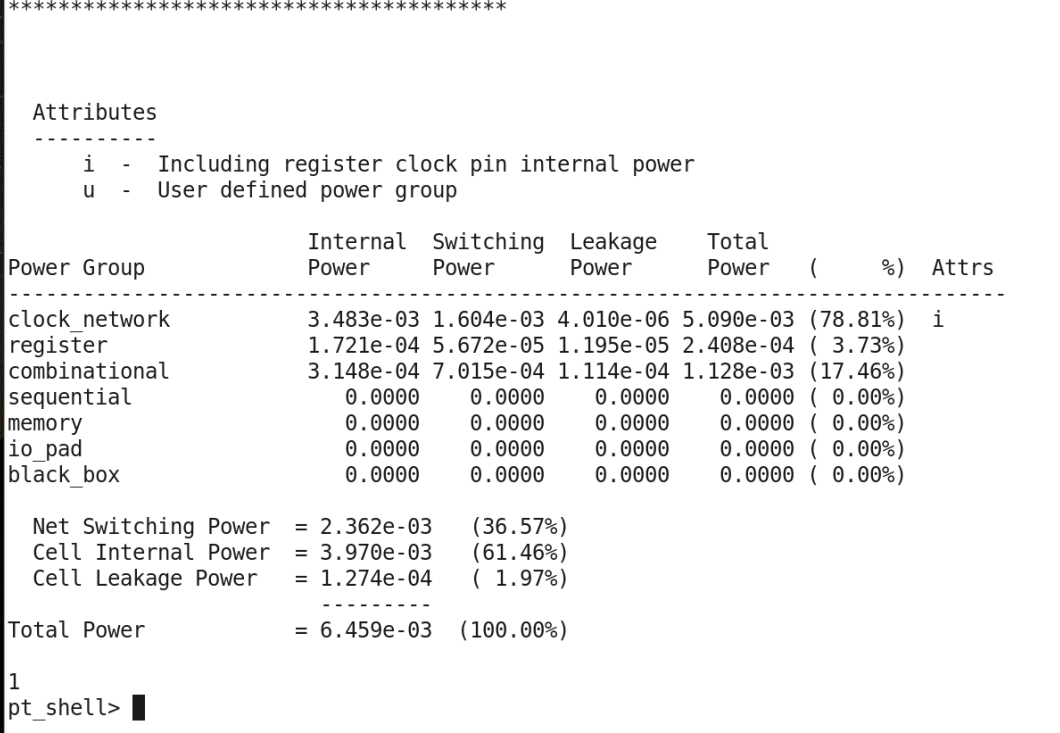

03 课程摘要 本次培训课程将以一颗数字芯片后端设计实现为目标,参训人员实际参与数字芯片后端设计完整过程,实际动手进行项目实践。 (一)主流的自动布局布线技术实训 本环节围绕五大方面对主流的自动布局布线技术展开实训。在布局布线的流程阶段,设计者需要确定各个模块的位置和连接方式,以实现电路的功能和性能要求。其次,布局规划和优化是布局布线过程中的关键步骤。它涉及到如何合理安排模块的位置和大小,以满足电路的性能和功耗要求。接电源规划则涉及到如何为整个芯片提供稳定的电源供应,以确保电路正常工作。时钟树综合可帮助设计一个高效的时钟网络,以确保时钟信号能够准确地传递到各个模块中。DRC修复可纠正由于违反设计规则而产生的错误,以确保电路的可靠性和稳定性。 (二)主流的静态时序分析技术实训 全面介绍静态时序分析技术,内容涵盖整个时序分析流程,包括电路的保持时间和建立时间计算,Timing Arc(时序弧)的概念与应用,以及如何处理多时钟域问题。此外,本环节还讲授设计约束分析,确保性能目标的实现,并探讨信号完整性分析,以维持高质量的信号传输。 (三)主流的低功耗分析技术实训 基于功耗分析基本概念和重要性的专业讲解,详细解读低功耗设计文件UPF的使用方法和作用,并深入探讨完整的功耗分析流程,包括功耗计算、IR drop(电压降)分析和EM(电磁兼容)分析等关键技术。通过实际案例讲解,具体描述如何优化芯片设计以实现低功耗目标,提高整体能效性能。 部分课件PPT截图 部分实训过程截图

04 课程安排 *培训前将提前给参训学员寄送纸质版课程讲义和开通设计平台账号。

Event Tags

Perhaps you'd be interested in

Question

All Questions

OrganizersMore

芯动力人才计划

芯动力人才计划®是工业和信息化部人才交流中心组织开展的、服务国家集成电路产业发展的人才专项。通过整合国内外优质智力资源,搭建园区、企业、人才等行业要素广泛参与、资源共享的交流平台,构建充满活力和富含价值的集成电路产业人文生态环境。 以业界应用需求为牵引,加强国际交流,为行业引入全球技术和国际化人才等要素资源;立足人才集聚和项目汇集,为园区实施创新驱动和产业集中提供保障;运用出国进修、研讨、讲座、大赛等方式,为人才职业发展和素质提升提供成长通道。与世界顶尖科研机构和著名跨国公司、高等院校如比利时IMEC、德国弗朗霍夫研究院、柏林工业大学、亚琛工业大学、英国剑桥大学、牛津大学、曼彻斯特大学、帝国理工大学、萨里大学、爱尔兰都柏林大学、美国麻省理工学院计算机中心、斯坦福大学、加州大学洛杉矶分校、IEEE、IBM、MICROSOFT、CISCO、芬兰NOKIA、瑞士洛桑国际学院、西班牙IESE商学院等长期开展合作。